# **Contents**

| 1       | Atom chip fabrication 3                                |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------|--|--|--|--|--|--|--|

|         | Ron Folman, Philipp Treutlein, and Jörg Schmiedmayer   |  |  |  |  |  |  |  |

| 1.1     | Introduction 3                                         |  |  |  |  |  |  |  |

| 1.2     | Fabrication challenges 4                               |  |  |  |  |  |  |  |

| 1.3     | The substrate 5                                        |  |  |  |  |  |  |  |

| 1.4     | Lithography 7                                          |  |  |  |  |  |  |  |

| 1.4.1   | Optical lithography 7                                  |  |  |  |  |  |  |  |

| 1.4.2   | Electron beam lithography 10                           |  |  |  |  |  |  |  |

| 1.5     | Metallic layers 10                                     |  |  |  |  |  |  |  |

| 1.5.1   | Deposition and etching 10                              |  |  |  |  |  |  |  |

| 1.5.1.1 | Electroplating 11                                      |  |  |  |  |  |  |  |

| 1.5.1.2 | Evaporation and lift-off metallization 13              |  |  |  |  |  |  |  |

| 1.5.1.3 | Wet and dry etching 14                                 |  |  |  |  |  |  |  |

| 1.5.1.4 | Designing potentials by post processing the wires 16   |  |  |  |  |  |  |  |

| 1.5.2   | Effects of roughness and homogeneity of the fabricated |  |  |  |  |  |  |  |

|         | structures 16                                          |  |  |  |  |  |  |  |

| 1.5.3   | Special metals 19                                      |  |  |  |  |  |  |  |

| 1.5.3.1 | Alloys 19                                              |  |  |  |  |  |  |  |

| 1.5.3.2 | Superconductors 20                                     |  |  |  |  |  |  |  |

| 1.5.3.3 |                                                        |  |  |  |  |  |  |  |

| 1.5.4   | Permanent magnets 24                                   |  |  |  |  |  |  |  |

| 1.5.5   | Metal outlook 26                                       |  |  |  |  |  |  |  |

| 1.6     | Additional features 30                                 |  |  |  |  |  |  |  |

| 1.6.1   | Planarization and insulation 30                        |  |  |  |  |  |  |  |

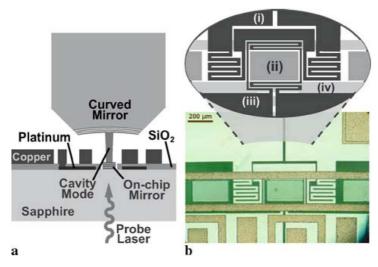

| 1.6.2   | On-chip mirrors 31                                     |  |  |  |  |  |  |  |

| 1.6.3   | Multi-layer chips 32                                   |  |  |  |  |  |  |  |

| 1.7     | Current densities and tests 35                         |  |  |  |  |  |  |  |

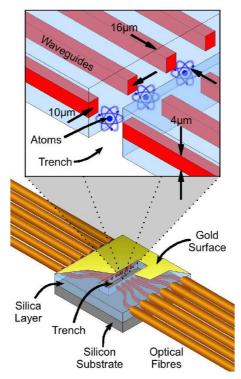

| 1.8     | Photonics on atom chips 37                             |  |  |  |  |  |  |  |

| 1.8.1   | Fiber-based integrated optics 38                       |  |  |  |  |  |  |  |

| 1.8.1.1 | SU8 - holding structures 38                            |  |  |  |  |  |  |  |

| 1.8.1.2 | Fiber-based fluorescence detector 39                   |  |  |  |  |  |  |  |

| 1.8.1.3 | Fiber cavities 40                                      |  |  |  |  |  |  |  |

# 2 Contents

| 1.8.2 | Micro lens and cylindrical lens 43           |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

| 1.8.3 | Micro disks and toroids 43                   |  |  |  |  |  |  |

| 1.8.4 | Mounted and fully integrated Fabry-Pérots 44 |  |  |  |  |  |  |

| 1.8.5 | Planar optics 46                             |  |  |  |  |  |  |

| 1.8.6 | Photonics outlook 48                         |  |  |  |  |  |  |

| 1.9   | Chip dicing, mounting and bonding 50         |  |  |  |  |  |  |

| 1.10  | Further integration and portability 52       |  |  |  |  |  |  |

| 1.11  | Conclusion and outlook 56                    |  |  |  |  |  |  |

| 1.12  | Acknowledgments 56                           |  |  |  |  |  |  |

|       | Bibliography 57                              |  |  |  |  |  |  |

|       |                                              |  |  |  |  |  |  |

#### 1

# Atom chip fabrication

Ron Folman, Philipp Treutlein, and Jörg Schmiedmayer

## 1.1 Introduction

One of the key promises of atom chips is the building of a robust quantum laboratory by miniaturizing and integrating quantum optics and atomic physics tools on a single device, on a chip [1–3]. This vision follows the path taken previously by the micro electronics and micro optics fields. The advantages and strengths of the specific field, in our case quantum optics in atomic systems, are combined with the technological potential of microfabrication and (large scale) integration to build a robust platform for implementation of quantum operations. An important ingredient in developing such an integrated, microfabricated approach to manipulating atoms, molecules or ions is the fabrication of the devices. The possibilities to combine vastly different technologies is thereby a key factor. This creates the technological basis for combining the best of the different quantum worlds of photons, atoms and solid-state in a single integrated quantum device.

This overview of atom chip fabrication is organized as follows: We first discuss the challenges to be faced when starting to conceive and fabricate chips for the (quantum) manipulation of atoms. We then describe the various ingredients and the corresponding fabrication methods. We focus not only on the currently most active and successful areas - current carrying wires and integrated photonics, but also look at more visionary approaches, examples being superconducting chips or the manipulation of atoms with real nano structures such as carbon nano tubes.

Here we explicitly discuss the material engineering and fabrication of atom chips for the manipulation of neutral atoms, but the same concept of robustness and versatility through miniaturization and integration can also be applied to manipulate (polar) molecules, ions, or trapped electrons.

#### 1.2

#### **Fabrication challenges**

In building atom physics based quantum devices on a chip, the challenge is not so much in micro and nano scale miniaturization, but rather in the integration of numerous technologies on the same device, and in the exceptional quality required from both the materials and the fabrication. Besides being UHV compatible, different requirements need to be addressed, depending on the specific application we have in mind.

- Current carrying wires are the workhorse of atom chips. Their key role is to provide magnetic fields for trapping and manipulation. These wires have to support high current densities, in some cases  $> 10^7$  A/cm² [4,5], many orders of magnitude larger than in a light bulb. Ultra cold atoms are extremely sensitive to variations in the magnetic potential. These can be caused by non uniform current flow in the wires. Current flow deviations of  $\sim 10^{-6}$  rad can be seen in 1d BEC experiments [6,7]. A deviation of  $> 10^{-4}$  rad makes a trap unusable for many experiments.

- Micro structured magnetic films and permanent magnets provide a very attractive way to create strongly confining micro traps at very high integration density [8–12]. One of the key issues in fabrication thereby is again the homogeneity of the magnetic materials [13].

- Radio-frequency (RF) and microwave (MW) fields complement the static magnetic trapping potentials [14–20]. Coupling two different ground states creates dressed state potentials similar to optical dipole potentials. The wire structures and the substrates need to be chosen well to support precise microwaves.

- Electric fields offer a route to detailed structuring and manipulation [21]. At the micron scale the substrates and the fabricated structures have to withstand the large electric fields created at even moderate voltages.

- Multi layer chips [20,22,23] are very instrumental. In an integrated atom chip, large structures (10 to 500  $\mu$ m) for the initial trapping and cooling of atoms have to be combined with functional structures on the (sub) micrometer scale to achieve controlled manipulation at a length scale where tunnel coupling between sites becomes important. Furthermore, the versatile application of electric and magnetic potentials requires the crossing of wires on the chip without contact.

- In many applications the chip surface needs to be a high quality mirror, be it for cooling and accumulating the atoms in a mirror MOT or for imaging atoms close to the surface. Furthermore, reflection of light

from the chip surface allows to integrate optical dipole traps and optical lattices on the atom chip [24]. This puts very stringent requirements on the quality of the mirror surface.

- By integrating micro optics and fiber optics on the atom chip [25, 26] one can incorporate optical micro manipulation and efficient detection of atoms. The fabrication methods for the optics have to be compatible with the other processes. Integrating fully tunable optical micro cavities pose an even larger challenge [27].

- Integration of superconducting elements on the chip will require compatibility with cryogenics.

- The atom chip is an ideal platform to integrate other solid state quantum devices like Micro-Electro-Mechanical systems (MEMs) [28,29], micro lenses and holes, miniature high finesse cavities, current carrying molecules or nano magnets, crystalline materials, etc. with the atomic physics on the chip. Connecting atoms to superconducting qubits [30,31] through circuit CQED [32, 33] will even require to go to mK temperatures.

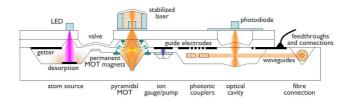

- Looking further into the future one can think of integrating more complex devices onto the chips like on board light and particle sources, miniature vacuum volumes and pumps, etc. (see last figure of this chapter) to build an independent stand alone device.

With all these diverse science possibilities each chip has an individual design, tailored to the physics and functions it is required to perform. What is needed is an interplay between physics, material engineering and fabrication, and compatibility of the methods.

## 1.3

#### The substrate

The substrate onto which the atom chip is fabricated has to be compatible with the different fabrication techniques needed to implement the chip design and has to guarantee the robust operation of the device. For a comparison of different substrate materials see Table 1.1.

In general the most important physical properties for present day atom chips stem from the fact that one of the key functions is to accumulate, cool and manipulate ultra cold atoms using static or oscillating fields. The substrate of the atom chip has to support the wires, provide electrical insulation between them, and dissipate the heat generated in the wires. Therefore, a substrate with high thermal conductivity, a high heat capacity, and an insulating surface is needed. A second important requirement, needed for smooth magnetic potentials, is the ease of high quality fabrication (few geometrical defects) and low wire surface roughness. This translates, for example, to very low surface roughness of the substrate.

A common substrate is a single crystal Si wafer in a (100) orientation with a thermal conductivity of  $\sim 150$  W/(mK) at room temperature. Wafers are typically  $\sim 500~\mu m$  thick and polished with very small surface roughness, sufficient even for the smallest wires. They can be cleaved with a diamond scorer. Neither the resistivity of Si nor the 2 nm native oxide layer on the substrate are sufficiently insulating for controlling DC currents at the  $10^{-5}$  level. Therefore the wafer is covered by a SiO2 insulation layer which provides a DC resistance of > 40 M $\Omega$  between the wires. Since SiO2 has a thermal conductivity of only 1.5 W/(mK), the insulating layer should be as thin as possible [5,34].

AlN is a non-toxic polycrystalline ceramic with an excellent heat conductivity of typically 180 W/(mK) at room temperature. Compared with Si, AlN is less brittle. It can be laser machined and easily cleaved with a diamond scorer. A polished AlN surface (specified surface roughness < 40 nm) has a significant residual roughness, with isolated defects of micrometer size. This is a problem if structures <  $10~\mu m$  are desired.

Both AlN and Si are common substrate materials for microwave circuits. AlN has a dielectric constant of  $\varepsilon_r = 8.7$  and a loss tangent of  $\tan \delta < 1 \times 10^{-3}$

| Material                       | Therm.          | Specific |                 | loss tang. | Linear                    | Density          | Optical    |

|--------------------------------|-----------------|----------|-----------------|------------|---------------------------|------------------|------------|

|                                | cond.           | Heat     |                 | 10 GHz     | expans.                   |                  | transm.    |

|                                | $Wm^{-1}K^{-1}$ | J/KgK    | $\varepsilon_r$ | $10^{-4}$  | $10^{-6} \mathrm{K}^{-1}$ | ${ m g~cm^{-3}}$ | nm         |

| BeO                            | 260-300         | 1000     | 6.7             | 30         | 8.4-9.0                   | 2.86             |            |

| AlN                            | 170-280         | 800      | 8.9             | 5          | 4.4-5.7                   | 3.25             | 500-3000   |

| Al <sub>2</sub> O <sub>3</sub> |                 |          |                 |            |                           |                  |            |

| Macor                          | 1.5             | 790      | 5.9             |            | 13                        | 2.52             |            |

| Sapphire                       | 35-40           | 700      | 9-11            | 0.2-0.8    | 5.8                       | 3.99             | 200-5500   |

| Alumina                        | 26-35           | 900      | 9.6             | 1          | 8.0                       | 3.9              |            |

| SiN                            | 10 - 16         | 690      | 10              |            | 3.3                       | 2.4              |            |

| SiO <sub>2</sub>               | 1.46            | 700      | 3.9             | 1-10       | 0.54                      | 2.2              | 180-2500   |

| BK7                            | 1.11            |          |                 |            | 8                         | 2.51             | 400-1400   |

| Pyrex                          | 1.13            |          |                 |            | 3.25                      | 2.23             | 300-2500   |

| Polyimide                      | 0.1-0.35        | 1090     | 3.4             |            | 30-60                     | 1.42             |            |

| Diamond                        | 900-2000        | 470      | 5.7             | 2          | 0.8                       | 3.52             | 400-300000 |

| GaAs                           | $\sim 55$       | 330      | 10.9-12.9       | <6         | 5.8                       | 5.3              | 1500-14000 |

| Si                             | 80-150          | 700      | 11.7            | <10        | 4.7-7.6                   | 2.34             | 1200-15000 |

| SiC                            | 350             | 690      | 10.8            | 30         | 4.8                       | 3.2              |            |

**Tab. 1.1** Room temperature properties of commonly used substrates for micro fabrication (data collected form a number of internet resources)

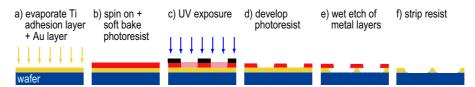

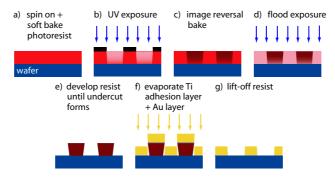

**Fig. 1.1** Process steps of optical lithography (see text). The example uses a contact mask, a positive resist system, and pattern transfer to the metal layer by wet etching.

at 10 GHz. If only DC currents are used in the experiment, Si of any doping level can be employed as the substrate material. For microwave applications, however, it is very important to choose high-resistivity Si to avoid strong dielectric losses. A typical wafer has a resistivity of  $\rho > 10^4 \Omega$ cm,  $\varepsilon_r = 11.9$ , and  $\tan \delta = 1 \times 10^{-3}$  at 10 GHz.

Other substrates commonly used in atom chip fabrication are GaAs, sapphire, alumina or  $SiO_2$ . Especially sapphire is interesting as a substrate for low temperature micro wave applications, where a loss tangent close to  $10^{-6}$  has been observed. Sapphire is also interesting when using light, as it is transparent in the visible light range.

## 1.4 Lithography

In lithography, a pattern is transferred into a layer of resist on the chip surface. The patterned resist is subsequently used as a stencil for etching or depositing material. An extensive discussion of lithographic techniques can be found in [35]. In the following, we give a brief introduction to optical and electron beam lithography, which are most commonly used for atom chip fabrication.

# 1.4.1 **Optical lithography**

In optical- or photolithography, light is used for pattern transfer from a mask to a light-sensitive resist. The spatial resolution is therefore set by diffraction of light. Optical lithography is a parallel process which allows large chips to be structured in short time, making it the dominant technique in the semiconductor industry. A typical photolithographic process involves several process steps as illustrated in Fig. 1.1: (a) substrate preparation – (b) spinning resist and soft baking – (c) exposure and postexposure treatment – (d) resist development – (e) transfer of the resist structure to the substrate – (f) resist stripping. In the following, we discuss this process in more detail.

**Masks for photolithography** — The photomask is a flat piece of glass (transparent to UV light) carrying a thin absorbing metal pattern (e.g. a 100 nm thick Cr layer) on one side. Depending on the resist system, the pattern on the mask is either a light field or dark field image of the structure to be fabricated. In research laboratories, the most common technique is contact lithography, where the metal pattern on the mask is in direct contact with the photoresist layer during exposure. A mask aligner is used to align mask and substrate with respect to each other and expose them to UV light (often, mercury lamps with spectral lines near 400 nm are used). The direct contact of mask and resist can result in defects. An alternative are projection masks, which are imaged by a high-resolution lens system onto the resist. Many commercially available masks are fabricated by laser lithography, i.e. by writing the pattern with a laser beam of  $\simeq 0.7 \ \mu m$  spot size into a thin resist layer on the mask. Masks with smaller structures can be written by electron beam lithography (see below). For coarse structures ( $> 50 \mu m$ ), the mask can be simply printed on a transparency. Laser lithography can also be used to avoid photomasks completely, by directly exposing the resist on each chip with the laser beam.

**Substrate preparation** — Lithography starts with a thorough cleaning of the substrate. Different (combinations of) wet or dry cleaning procedures are used, involving e.g. organic solvents in an ultrasonic bath, or a strong acid such as H<sub>2</sub>SO<sub>4</sub>, or an acid-oxidant combination (e.g. 'piranha etch'), or oxygen plasma cleaning. Subsequent to cleaning, some processes require deposition of homogeneous insulating and/or metal layers on the substrate. In the example of Fig. 1.1, the substrate is covered with a thin Ti adhesion layer and a gold layer, which will later be patterned by wet etching.

**Spinning resist and soft baking** — A spin coater is used to apply a photoresist layer of a desired thickness (ranging from a few 100 nm to a few 100  $\mu$ m, depending on the resist system and application). The photoresist is an organic polymer sensitive to UV radiation. After spin coating, the resist layer is soft baked (prebaked) to remove solvents and promote adhesion to the substrate.

**Exposure and postexposure treatment** — The resist-coated substrate is aligned with respect to the photomask and subsequently illuminated with a well defined intensity of UV light for a controlled duration (typically a few seconds). Finding the proper exposure dose is an important task during optimization of the process. The UV light induces a chemical reaction in the exposed areas of the photoresist, altering the solubility of the resist in a solvent. If a *positive resist* is used, the exposed areas are rendered soluble. In a *negative resist*, the exposed areas are rendered insoluble. After exposure, certain resists require further treatments. For example, an *image reversal resist* requires a post-exposure bake and subsequent flood exposure with UV light, thereby turning the originally positive resist into a negative one. The choice of the resist system for a given application depends on many parameters, such as the

desired spatial resolution and resist thickness, the desired shape of the resist profile (positive vs. negative slope of the resist sidewalls, see section 1.5), and the chemical stability in subsequent processing steps.

**Resist development** — During development, the resist is selectively dissolved, usually by submerging and agitating the substrate in a liquid developer solution. This transforms the latent image formed during exposure into a resist pattern that will serve as a mask in further deposition or etching steps. Careful control of the development time and developer temperature is required to reproducibly obtain the desired resist profile. A mild oxygen plasma treatment can be useful to remove unwanted resist left behind after development. Furthermore, some applications require postbaking of the developed resist to improve stability.

**Transfer of the resist structure to the substrate** — Various methods exist to transfer the resist structure to the substrate, and the most common ones for atom chip fabrication are discussed in section 1.5 below. In the example of Fig. 1.1, wires are defined by a wet etch of the metal layers with aqua regia.

**Resist stripping** — In the last step of the photolithographic process, the resist is removed (stripped). Similar to the procedures for substrate cleaning, a sequence of steps involving organic solvents, acids, acids+oxidants, or plasma cleaning is used. The additional requirement is that the chemicals and procedures employed should not attack the desired structures.

**Spatial resolution** — The spatial resolution of contact lithography is limited by the near-field diffraction of light at the structures in the mask and thus decreases if there is a gap between the mask and the substrate. Consider photoresist of thickness t exposed with light of wavelength  $\lambda$  through a mask with a pattern of equal lines and spaces of periodicity 2w. The theoretical resolution, i.e. the minimum linewidth resolved, is given by  $w_{\min} = (3/2)\sqrt{\lambda(g+t/2)}$ , where g is the gap between resist and mask [35]. To obtain high resolution, g has to be as small as possible. This means that edge beads and defects of the photoresist have to be avoided. The substrate has to be pressed against the mask. In a multi-layer process, the topology of the lower layers (if not planarized perfectly) will introduce gaps and thus decrease resolution. As an example, consider  $\lambda = 400$  nm,  $t = 1.5 \mu m$ , and g = 0, which yields  $w_{\rm min} = 0.8 \ \mu \rm m$ . In practice, achieving such high resolution is possible, but challenging. Routinely,  $w > 2 - 3 \mu m$  is achieved.

Resist bleaching is a phenomenon that allows one, to some extent, to enhance resolution beyond  $w_{\min}$ . During exposure, the resist becomes more transparent to the illuminating light. This allows one to define narrow features in thick resist, i.e. the fabrication of structures with high aspect ratio.

#### 1.4.2

### Electron beam lithography

Electron beam lithography allows one to fabricate significantly smaller structures than optical lithography. Moreover, the electron beam has a large depth of focus, facilitating patterning of substrates with uneven topography. Ebeam lithography is a serial technique in which a narrow electron beam is scanned across a resist layer pixel-by-pixel. The resolution is limited by electron scattering in the resist and substrate to typically 10-100 nm, depending on resist thickness. The standard positive resist is polymethylmethacrylate (PMMA). Electron bombardment breaks the PMMA into fragments, the resulting shorter polymer chains are dissolved faster during development. Negative resists and multi-layer resist systems are available as well.

E-beam lithography is slow, and writing a complex pattern can easily take several hours, making the system prone to drifts and vibrations. Moreover, the size of the field that can be written without moving the substrate is typically only a few hundred  $\mu$ m, for larger areas stitching is necessary. Nevertheless, the superior resolution make e-beam lithography the method of choice in many applications. The basic steps involved in an electron beam lithography process are similar to those discussed in the previous section. During exposure with the e-beam, the substrate is mounted in a vacuum chamber. No physical mask is needed, the pattern is defined in computer software.

Optical and electron beam lithography are often combined. The smallest and most critical structures in the chip center are defined by electron beam lithography, while optical lithography is used in a separate process step for uncritical 'large-scale' structures such as lead wires and contact pads at the edge of the chip.

#### 1.5 Metallic layers

Metallic wires, electrodes, or permanent magnets are the most commonly used structures on an atom chip. In the following we introduce the most important deposition and etching techniques used for the patterning of normal metals, discuss issues of roughness and homogeneity of the structures, and review the fabrication of structures out of special metals such as alloys, superconductors, semiconductors, and permanent magnets.

#### 1.5.1

## **Deposition and etching**

Resist patterns created by lithography can be transferred to the substrate by *additive* (deposition) or *subtractive* (etching) techniques. The two most com-

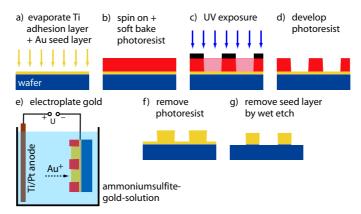

Fig. 1.2 Electroplating. The process steps are explained in the text.

monly used techniques for the fabrication of atom chip wires are additive techniques: electroplating and lift-off metallization.

#### 1.5.1.1 Electroplating

Electroplating was among the first techniques used for atom chip fabrication [4,36]. In this technique, the chip serves as the cathode of an electrolytic cell. Resist structures on the chip form a mold for the electroplated metal. Under an applied voltage, metal ions from the plating solution deposit on the areas not covered by resist. The amount of deposited material per unit time is controlled by the current flow. Electroplating is more time and material efficient than metal deposition through thermal evaporation or sputtering. It is therefore well suited also for structures with a thickness  $\gg 1\mu m$ . Furthermore, structures with high aspect ratio (wire height comparable to or higher than width) are easier to fabricate than with lift-off or etching techniques (see below). Electroplating is very versatile, it can also be used to fabricate vias and other non-planar structures [35]. A review of electroplating can be found in [37,38], and its application to atom chips is discussed e.g. in [39–41].

Fig. 1.2 illustrates a basic gold electroplating process (a detailed recipe can be found in [41]). (a) After substrate cleaning, a 2 nm Ti adhesion layer and a 50 nm Au seed layer are deposited by thermal evaporation. This layer serves as the cathode. (b) The chip is spin coated with a 6.5  $\mu$ m thick layer of photoresist and subsequently patterned by optical lithography (c+d). The resist structures should be slightly taller than the desired thickness of the wires. In our example, a positive tone resist with high pattern stability in acidic and alkaline plating baths is used.

In the following electroplating step (e), the chip and a Ti/Pt mesh anode are connected to a power supply and submerged in 1 liter of electro-

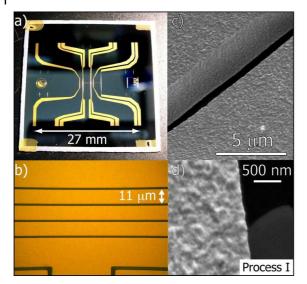

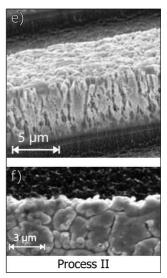

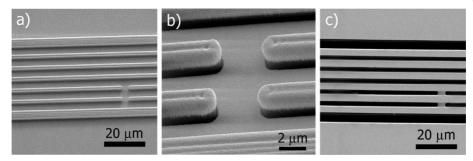

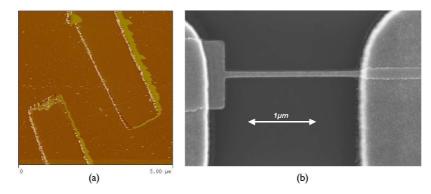

**Fig. 1.3** Electroplated gold wires fabricated with two different processes. (a)-(d) Wires of 5  $\mu$ m thickness on a Si chip, fabricated with the process of [41]. (a) Entire chip with contact pads. (b) Close-up of (a). The gaps between wires are 3  $\mu$ m wide. (c)+(d) SEM pictures of the wires. The grain size of the gold is 200 nm, the r.m.s. surface roughness is 15 nm. (e)+(f) For comparison, SEM pictures of wires fabricated with the process of [42] are shown (thickness 4.5  $\mu$ m). Grains of micrometer size are visible, the r.m.s. roughness is 200 nm.

plating solution, whose temperature is carefully controlled in a water bath. In our example, a solution from Metakem is employed, which is based on ammoniumsulfite-gold(I) ([ $(NH_4)_3Au(SO_3)_2$ ]). It is commonly used for dentistry and jewelery and yields very smooth gold deposits of 99.99% purity. To deposit gold, the desired plating current I is driven through the electrolytic cell. Stirring helps to avoid local depletion of the solution and thus ensures a more homogeneous gold layer. The thickness h of the gold layer deposited after a time t can be determined by Faraday's law:  $h = \alpha \frac{ItM}{nFSo}$  $1.1 \times 10^{-10} \frac{\text{m}^3}{\text{As}} \times \frac{It}{\text{S}}$ , where M the molar mass and  $\varrho$  the mass density of gold, F is Faraday's constant, n=1 is the charge of the gold ions, and  $\alpha \approx 1$  the current efficiency for gold plating. The surface area S of the deposited gold film is given by the surface area of the wire layout plus the contact pads and connectors. In the parallel plate configuration, the current density is approximately constant over the exposed gold areas of the chip. (f) After the wires are electroplated to the desired thickness, the resist is stripped. In the final step (g), the Au seed layer and the Ti adhesion layer are removed by a wet etch with aqua regia. This isolates the electroplated wires from each other. The gold etch also attacks the wires, increasing surface roughness. It is therefore

Fig. 1.4 Lift-off sequence with an image reversal resist. Gold is deposited by e-beam evaporation. The process steps are explained in the text.

desirable to work with a seed layer as thin as possible. Figs. 1.3(a)-(d) show electroplated gold structures on Si chips fabricated with this process.

The quality of the electroplated wires crucially depends on the choice of the plating solution and on the process parameters. Different solutions (and also the same solution at different process parameters) deposit gold of very different grain size [38]. Moreover, the complex bath chemistry can be disturbed by contaminants. Some processes result in deposits with micrometer grain size [42], resulting in inhomogeneous current flow in the wires and thus roughness of the generated potentials. Optimized electroplating processes, however, result in structures with very low roughness [39,41]. In Fig. 1.3(c)-(f), SEM pictures of electroplated gold wires fabricated with the processes of [41] and [42] are shown in comparison. The roughness of the wires of [41] is about one order of magnitude smaller than that of [42].

#### 1.5.1.2 Evaporation and lift-off metallization

Evaporation and lift-off metallization is a standard technique for fabricating metal structures of high quality [35]. In this technique, patterned resist acts as a mask for evaporated gold. After removal of the resist ("lift-off"), only the desired gold structures remain on the chip. Gold layers deposited by thermal or electron-beam evaporation often have smaller surface roughness than electroplated wires. This is important for generating smooth trapping potentials for waveguides or 1d traps [43] and for using the wire layer simultaneously as a mirror [44] for a mirror-MOT [36]. Evaporation allows very precise control over the thickness of the deposited material. However, the thickness is limited by the slow deposition rate and substantial material consumption to a few  $\mu$ m at maximum. An alternative for thicker structures is sputtering of the metal, or electroplating (see previous section). Evaporation and lift-off was adapted to atom chip fabrication as described in [5, 23, 40, 41, 45].

An example of a lift-off sequence is illustrated in Fig. 1.4 (a detailed recipe can be found in [41]). (a) The substrate is spin-coated with a 1.6  $\mu$ m thick layer of photoresist. An image reversal resist is used, which allows one to create resist sidewalls with a negative slope ("undercut"), which is crucial for lift-off metallization. (b) The resist is exposed for a few seconds with UV light through a mask which bears a negative image of the wires to be fabricated. Due to the small exposure dose, the resist is not fully exposed down to the substrate. This leads to the negative slope of the resist sidewalls after image reversal and development. (c) An image reversal bake on a hot plate at a carefully controlled temperature cross-links the resist in the exposed areas and thus renders it insoluble in the developer and insensitive to further exposure. (d) Subsequently, the chip is flooded with UV light, which now renders the previously unexposed areas soluble. (e) These areas are removed during development. The development time is carefully adjusted to control the formation of the undercut. Residues of photoresist are removed by a short oxygen plasma cleaning step. Subsequent baking of the resist structures on a hot plate improves resist stability. (f) A 1  $\mu$ m thick layer of gold is deposited on top of a 3 nm thick Ti adhesion layer by e-beam evaporation in a UHV evaporation chamber. The resist acts as a mask for the gold, while the undercut prevents gold in the resist trenches from sticking to gold on top of the resist. (g) Lift-off is performed in a bath of hot acetone. This removes the resist and the gold on top of it and leaves behind the desired structures. If necessary, lift-off can be forced by agitation or by mild ultrasound.

For successful lift-off, the resist layer should be somewhat thicker than the thickness of the deposited gold layer. The resist undercut can be adjusted by changing exposure time, image-reversal temperature, and development time. A strong undercut can be seen in an optical microscope as a bright outline of the resist edges. However, for very small periodic structures, mechanical and thermal stability of the resist requires that development be stopped before the bright outline is visible. For process optimization, the undercut can be observed with an electron microscope, see Fig. 1.5.

Fig. 1.6 shows wires that were fabricated by evaporation and lift-off [5,41]. The surface and edge roughness of the wires is small, resulting in very smooth magnetic potentials. Moreover, the gold wire layer can serve as a high-quality mirror if the gaps between the wires are sufficiently narrow.

## 1.5.1.3 Wet and dry etching

The simplest subtractive technique is wet etching, which is illustrated in Fig. 1.1 above. After the resist has been patterned, the chip is submerged and agitated in a suitable etchant (aqua regia in the case of gold wires), which removes the metal layer in the areas not covered by the resist. Wet etching results in relatively rough wire edges. Moreover, the metal is removed isotropi-

Fig. 1.5 SEM images of gold wires before and after lift-off. (a) Resist structure with deposited gold on top. (b) Close-up of (a), the undercut of the resist sidewalls is visible. (c) Gold wires remaining after lift-off.

Fig. 1.6 SEM images of micrometer-size atom chip wires fabricated by evaporation and lift-off. (a) Gold wire, 1  $\mu$ m thick and 1.7  $\mu$ m wide [41]. The grain size of the gold is  $\sim 100$  nm, the r.m.s. surface roughness is 3 nm. (b)+(c) Gold wires of [5] with 50 - 80 nm grain size.

cally, and wet etching is thus not suitable for fabricating structures with steep side walls and high aspect ratio. By contrast, some dry etching techniques such as reactive ion etching [35] are very anisotropic, and can thus be used to fabricate high aspect ratio structures with steep edges. Brute force ion etching (called ion beam milling) may also be used if a thin layer of metal needs to be etched and the lift-off method is not feasible, for example, when high evaporation temperatures are used (e.g. if one needs large grain size), and the resist may only be put after the evaporation process (this method has been used in [7]).

For wet and dry etching, it is essential to choose an etchant that effectively removes the material to be patterned, but leaves intact additional structures on the chip and the functionality of the etch mask. The etch mask does not have to be a resist structure, it can also be a suitable patterned metal or dielectric layer. Two very useful papers with hundreds of etch rates for a large number of materials in different wet and dry etches are Refs. [46, 47]. They are also useful for choosing the right chemicals for cleaning and resist stripping tasks.

Besides etching, subtractive patterning techniques include focused ion beam milling (see the next section), which can be used to structure arbitrary materials, and laser machining, which is useful e.g. for hole drilling. These techniques differ from etching in that they do not require a physical mask.

#### 1.5.1.4 Designing potentials by post processing the wires

In general the magnetic potentials on atom chips are formed by the subtraction of two (large) magnetic fields, the field of a current carrying wire and a (homogeneous) bias field (see other chapters in this book). The value of the magnetic field at the potential minimum  $\delta B_{min}$  is determined by the angle between the field of the wire and the bias field. A small change of the current direction results in a significant change in the trapping potential. A deviation of the current flow by  $\vartheta \sim 10^{-5}$  rad can lead to  $\delta B_{min} \sim 1$  mG which corresponds to 67 nK for trapped Rb atoms.

One can implement slight changes in the current path deliberately by sculpturing the bulk of a lithographically patterned plane conductor [48] and thereby fine tune or even design local features in the trapping potential. The contributions of a current flow pattern with wave vector k to the magnetic field are exponentially damped with height z as  $e^{-kz}$  when receding from the wire. Therefore, in order to achieve a modulation of a fraction  $\eta_0$  of the maximum achievable field at a minimum structure size  $\lambda_{min} = 2\pi/k_{max}$  one has to stay at distances of  $z < -\frac{\log \eta_0}{k_{max}}$  (for details see [48,49]).

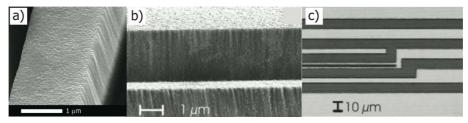

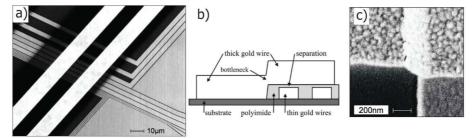

This post processing of the chip structures can be done with a Focused Ion Beam (FIB) technique [50], which allows to create modifications with high precision (< 20 nm) and large aspect ratios (height/width > 30). The Heidelberg/Vienna group experimentally demonstrated the power of this technique by sculpturing a 10  $\mu$ m wide and 2.5  $\mu$ m thick gold conductor on a Si substrate [48,51] (Fig. 1.7).

### 1.5.2

## Effects of roughness and homogeneity of the fabricated structures

A small change of the current direction results in a significant change in the trapping potential. Irregular current flow will result in uneven potentials with significant roughness.

After the first creation of a BEC on an atom chip a number of groups observed large roughness in the magnetic potentials holding the atoms. In many cases even a 1  $\mu$ K thermal cold atom cloud was fragmented into many components when approaching distances below 100  $\mu$ m from the wire [52–56]. This potential variation originates from inhomogeneous magnetic field components  $\Delta B$  in the direction parallel to the current carrying wire [57] and can be attributed to variations in the current flow direction in the chip wires. Common to all but one of these experiments was, that they used electro plated wires to hold the trapping currents (the experiment by the Sussex/Imperial

Fig. 1.7 Examples of wires sculptured by FIB a) Double well created by making two 1  $\mu$ m deep, 0.2  $\mu$ m wide cuts in opposite edges of a trapping wire. b) Polishing the wire edge as imaged by the FIB itself. The polished region (on the right) is smoother and reveals details of the structure of the gold wire. The contrast in the image is given by the ion reflection coefficient, varying with the relative orientation of the crystal axes of the gold grains. The picture shows a small region of 9.2  $\mu$ m imes 5.1  $\mu$ m at the end of the polished section. c) Magnetic lattice with periodicity a=4  $\mu$ m created by a string of holes with diameter D=a/2 in a wire with thickness d=a/2 and width w=10  $\mu$ m. Top: Current density  $j_y$  in the transverse direction. Center: The potential modulation V at a height of z=6  $\mu$ m, scaled to the characteristic energy  $E_r = \hbar^2 k_a^2 / 2m_{Rb}$  (lattice vector  $k_a = 2\pi/a$ ). Bottom: The potential along the lines drawn in the central image. The maximum modulation with a peak-to-peak depth  $V_0 \simeq 20\,E_r$ , is obtained at y=2  $\mu$ m (orange continuous curve) while  $V_0 \simeq 6 \, E_r$  for y=5  $\mu$ m (blue dashed curve).

College group used a drawn copper wire [54]). In an experiment by the Orsay group, the large potential roughness observed was clearly identified as coming from the rough edges of the fabricated wires, and the model of Wang et al. [58] provided a full quantitative explanation [55,56]. In many cases the observed modulations were so strong that they prevented the creation of a continuous elongated BEC.

At about the same time in 2003 it became clear that this is not the general case. Such strong potential roughness was not found in the experiments at Heidelberg [43,59] using atom chips with gold wires evaporated on a Si substrate and structured by the lift-off technique [5]. Nevertheless, a very small potential roughness remains which is also magnetic in origin. Measurements of the potential landscape over the whole width of a 100  $\mu$ m wide wire, by scanning the position of the condensate across the wire using the BEC mag-

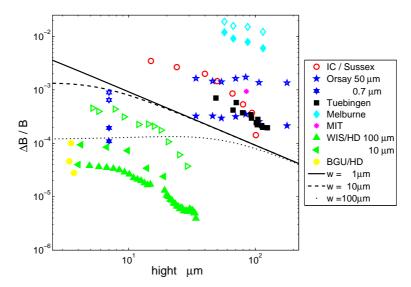

Fig. 1.8 Comparison of different atom chip potential roughness measurements. Data is taken from figures in the published literature and PhD theses and displayed with color codes according to the experimental group. Filled symbols denote rms values, and data displayed as open symbols are peak to valley maximum height of the roughness. Sussex: data from a gold coated copper wire [61]; Orsay: data from an electro plated wire [55, 56], and recent data from a 5 wire setup on an evaporated gold chip; Tübingen: data from electroplated wires (PhD thesis, J. Fortagh); *Melbourne*: data from a permanent magnet atom chip [13]; MIT: data from electro plated wires; WIS/HD: data from the analysis chips fabricated at the Weizmann Institute of Science: a 100  $\mu$ m wire [43], 2003 data from various 10  $\mu$ m wires [59, 62]. The open triangles give the peak to valley of the worst ever roughness observed in HD: a 10  $\mu$ m wire (PhD thesis, L. Della Pietra). BGU/HD: Recent data from 3 different wires fabricated at Ben-Gurion and analyzed in HD [7].

netic field microscope [6,60], show no significant increase near the wire edges. A detailed analysis clearly showed that the edge roughness model can not explain the observed potential variations [43,59].

Even more surprising are the findings of Aigner et al [7] where the current flow in 3 different wires with different grain size and wire thickness was probed. The measurements showed that the thinnest wire with the largest grains had the smoothest current flow. A detailed analysis of the measured potential landscape and a comparison to the surface roughness of the gold layer clearly show that the local properties of the metal, and not imperfections in the wire boundary are the key to the current flow variations in the wires with the smoothest potentials [63].

It is interesting to compare the potential roughness observed on different chips and in different experiments. In most applications of atom chips an important parameter is how large the potential roughness  $\Delta B$  is in comparison to the energy scale of the transverse confinement  $\omega_{\perp}$ . A stringent requirement for 1d experiments is  $\hbar\omega_{\perp}\gg\mu\Delta B$ , where  $\mu=\mu_Bg_Fm_F$  is the magnetic moment of the trapped atomic state. The magnetic confinement  $\omega_{\perp} \propto d^2 B/dr^2$ is determined by the magnetic field gradient dB/dr and the longitudinal Ioffe field  $B_{\text{Ioffe}}$ . To achieve the same ratio  $R_{\omega\perp} = \mu \Delta B / \hbar \omega_{\perp}$ , the allowed relative magnetic field roughness for a trap built at height h above a flat wire of finite width *w* scales like:

$$\frac{\Delta B}{B} < R_{\omega \perp} \frac{2w}{(w^2 + 4h^2)(\frac{\pi}{2} - \arctan[\frac{2h}{w}])} \sqrt{\frac{\mu_B g_F m_F}{M B_{ip}}}$$

(1.1)

Fig. 1.8 shows a comparison of a large variety of measured potential roughness data from many different laboratories.

1.5.3

#### **Special metals**

#### 1.5.3.1 Alloys

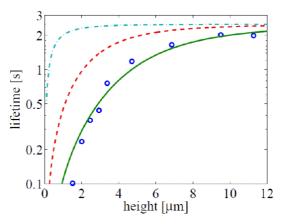

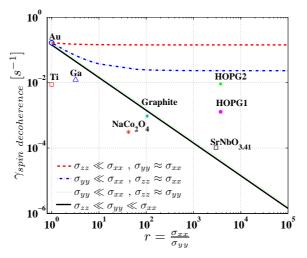

One of the high priority goals in atom chip research is the increase of lifetime and coherence time for ultracold atoms trapped in magnetic potentials close to the surface. This is important for both scientific aims and technological applications. Progress towards this goal demands the control and reduction of magnetic noise produced by the metallic components of the atom chip. Randomly fluctuating magnetic fields are generated by thermal current noise in the conducting chip elements and reduce the number of trapped atoms (losses), increase their temperature (heating) and lead to a phase uncertainty in the atom's state (decoherence) - see, for example, [64] and references therein. Theoretical analysis of the magnetic noise generated by a normal metal [65–68] predicts a fast reduction of the lifetime  $\tau$  with the decrease of the distance  $z_t$  between the trapped atom and the metal surface (trap height); this is in excellent agreement with lifetime measurements [61, 69, 70]. At a trap height less than  $10 \div 20 \,\mu\text{m}$ , thermal magnetic noise may exceed all other harmful influences on the atom cloud (technical noise due to the current supply instability, residual gas collisions, stray magnetic fields) and could present the dominant limit for the lifetime.

As is well known by now following the work of Carsten Henkel (see the corresponding chapter in this book), cooling of normal metals such as gold or copper will not reduce the harmful effect of thermally induced noise on the atoms. Hindering processes such as spin-flip (reducing trap lifetime), heating and decoherence will thus not be suppressed by cooling the atom chip. The reason for this rather counter intuitive behavior has to do with the fact that the strength of the relevant magnetic noise is proportional to  $R=T/\rho$  where T is the metal surface temperature and  $\rho$  its resistivity. As  $\rho$  is typically linearly dependent on T (due to phonon scattering) R does not become smaller with dropping temperatures and typically even becomes larger. As presented in the next section, superconductors are expected to have much smaller noise, but on the other hand present other challenges such as sensitivity to external magnetic fields and inhomogeneous current distribution. The question therefore arises if one may find a material where on the one hand cold temperatures do lower the level of R and on the other, a simple material is used.

Indeed alloys have such features. On the one hand they are a simple metal easily deposited (e.g. with sputter), with no sensitivity to external magnetic fields and with an homogeneous current distribution, and on the other their R drops with dropping temperatures. The reason for this behavior lies in the special dependency of  $\rho$  on T in alloys. At low temperatures, resistivity due to imperfections and impurities, if large enough, may become dominant over that dependent on phonon scattering. Alloys have impurities and hence the resistance becomes a constant at low temperatures. This is explained in detail in Ref. [71], which also presents the data for numerous metals. As an example of the benefits of such a material, we present in Fig. 1.9 how the spin flip rate behaves as a function of distance to the surface. The fact that such a simple choice of material may make a difference of up to two orders of magnitude in the lifetime, shows clearly the important role material engineering can play in atom chips.

#### 1.5.3.2 Superconductors

In the last few years, the application of superconducting materials to atom chips has been widely discussed as a perspective to extend the lifetime of cold atoms [68,73–76]. A recent theoretical estimate [75] of the magnetic noise caused by a superconductor in the Meissner state showed that the lifetime of atoms trapped above a superconducting layer would be, at least, six orders of magnitude longer than above a normal metal in the same geometry. The analysis presented in [76] predicts an atom lifetime of 5000 s at a trap height of 1  $\mu$ m. For comparison, at the same height in a normal metal trap the lifetime is less than 0.1 s [70].

Details of experiments with superconductors may be found in ??. Here we give a brief account with emphasis on fabrication. Two first realizations of atom chips with superconducting elements have been reported in Refs. [77,78] and [79]. In both setups, the trapped atoms were  $^{87}$ Rb. In the Paris experiment, the current-carrying wires (in "U" and "Z" shape) were made of niobium and operated at about 4.2 K. The obtained atom spin relaxation time  $\tau_s$

Fig. 1.9 Comparison of trapping lifetimes of <sup>87</sup>Rb atoms above a copper wire on an atom chip [70] with a theoretical calculation (solid line) - taken from [71]. Predicted lifetimes are also shown for a similar wire made of an alloy of Ag with 5.5% Au content, cooled down to T=77K (dashed) and 4.2 K (dash-dotted). Note that the calculation in [71] differs from the one made in [70]. Van der Waals forces are not taken into account. Let us also mention that the maximum noise reduction factor of 75 is not visible, due to the affect of the technical noise and/or background gas collisions limiting the lifetime in this experiment to a maximum of  $\tau_{\text{tech}} = 2.5 s$  [72].

was estimated as 115 s. This value is comparable to the best one achieved for atoms trapped near normal-metal wires [80]. In the second experiment [79], special efforts have been undertaken to reduce the influence of technical noise. Utilizing a MgB2 film, a "Z"-shaped wire was fabricated as a part of a closed superconducting loop and operated in the persistent current regime. This permits to disconnect the current supply and get rid of its instability i.e. technical noise. To our knowledge, in both experiments the trap lifetimes were limited by processes other than the magnetic noise generated by the superconducting elements of the atom chip. Furthermore, to the best of our knowledge, to date no atoms were taken in these two experiments to a distance below a few tens of *µm* from the surface.

The Paris atom chip was made on a 65 mm x 30 mm silicon wafer (thickness 360  $\mu$ m) with a 500 nm insulating oxidized layer. It was coated by a 900 nm thick layer of Nb by cathodic plasma sputtering. A "U"-wire (width 280  $\mu$ m) is used for the on-chip mirror-MOT, and a "Z"-wire (width 40  $\mu$ m) for the magnetic Ioffe-Pritchard trap. The cross section of the "Z" wire was 40 x 0.9  $\mu$ m<sup>2</sup>. The wires and contact pads are produced by standard optical lithography with a laser-printed mask followed by reactive ion etching. The resulting wire edge precision is about 5  $\mu$ m. A gold layer of thickness 200 nm was deposited on the niobium wire to increase its reflection. The current through the "Z" wire reached 1.5 A, close to the critical current value of 1.94 A. The critical current density obtained for the niobium wire was  $J_c \approx 5 \times 10^6$  A/cm<sup>2</sup> at 4.2 K.

In the Japanese group, a magnesium diboride MgB<sub>2</sub> film of 1.6  $\mu$ m thickness was grown by molecular-beam epitaxy (MBE) on a sapphire C substrate (10 x 10 x 0.5 mm). The cross section of the "Z"-wire was 100 x 1.6  $\mu$ m<sup>2</sup>. The persistent superconducting current of I=2.4 A in a "Z"-structure was significantly lower than the critical value of  $I_c\approx 16$  A (the critical current density at 4.2 K is about  $J_c\approx 10^7$  A/cm² and the transition temperature of MgB<sub>2</sub> is  $T_c\approx 35$  K). The top of the MgB<sub>2</sub> thin film was coated with a thin gold layer to prevent radiation heating and for better reflection. The circuit pattern on the chip was produced by removing the unnecessary part of the MgB<sub>2</sub> thin film by ion milling. This group has also demonstrated trapping atoms on a Nb film [81].

Recently, two additional groups joined the experimental effort: In the Singapore group, an atomic interferometer was created on the basis of a high- $T_c$  superconducting film [82,83]. The YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7- $\delta$ </sub> (YBCO) film was grown by epitaxy on a yttria- stabilized zirconia (YSZ) single crystalline substrate. The lattice constants of YBCO and YSZ are matched, allowing homogeneous growth of the superconducting material. The final thickness of the YBCO film was 600-800 nm. On top of the YBCO film a 200 nm thick layer of gold was deposited to protect the superconducting material. Structuring of the chip is performed by two different techniques. These are standard optical lithography followed by a wet-chemical etching as well as direct femto-second (fs) laser ablation. The standard lithography procedure has a resolution limit of about  $1\mu$ m for the structure size. With the fs-laser ablation procedure the desired patterns on the chip are realized by locally removing the gold and YBCO layers with focused laser pulses (2 µJ, 130 fs, center wavelength 800 nm), resulting in insulating regions between the superconducting structures. In this laser assisted structuring technique, it is crucial that the film is not heated. In case of heating, oxygen would be lost and the superconducting properties of the thin film would degrade. This requirement sets the demand for using fslaser pulses and may at times set the wet etching as the preferable method. In the final chip, the roughness of the surface was almost negligible with an rms value of the surface height of only 2.3 nm. The critical current density  $I_c$  at liquid nitrogen temperature was 2 MA/cm<sup>2</sup>. Recently, this group has managed to trap atoms in the field of a vortex [84].

In the Tübingen group [85], a cylindrical niobium wire of diameter 0.125 mm has been used. The wire was mechanically clamped to copper plates firmly attached to a helium cryostat. From the published data one may assume that the small distance of about 25-30  $\mu$ m was achieved between the atoms and the super current (where one has to take into account the super current radius for each temperature).

Aside from low thermal magnetic noise, the application of superconductors in atom chips may be advantageous also due to high current densities without Joule heating, and practically zero electric fields across the superconducting elements. In addition, as noted, technical noise can be reduced by inducing a persistent current. Hence there is significant motivation to make available simple fabrication procedures for superconductors. Recently, two works have analyzed in detail the trapping parameters of cold atoms in magnetic traps made by type I and type II superconductors [86,87].

#### 1.5.3.3 Semiconductors

In the future, atom chips might be built like integrated circuits from a single semiconductor substrate. For example, the current used for trapping and manipulating atoms will flow in an epitaxially grown layer, that is covered by an insulating layer on top. Such an approach has the advantage that the epitaxially grown material is more uniform and better controlled than the wires deposited onto the surface. In addition, such a structured semiconductor atom trap may be used to probe the current flow in the semiconductor, by using the cold atoms as a magnetic field microscope [6,7,60].

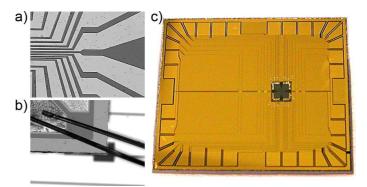

First steps to develop a semiconductor based atom chip were carried out by the Heidelberg/Weizmann team [34]. The chips were fabricated from a GaAs wafer grown using molecular beam epitaxy (MBE) at the Weizmann Institute of Science. Such a chip contains a super lattice of twenty layers of GaAs and AlGaAs which are used as an etch stop layer for selective etching. On top of it, about one micron of Si doped (n+) GaAs is grown as a conductive layer. The measured 3d charge carrier density is  $N \sim 6.4 \times 10^{18}$ , the mobility is  $\mu = 1160$ cm<sup>2</sup>/V sec, and the 2d resistivity of this layer is 8.5  $\Omega$

The wire structures are then fabricated into the GaAs wafer by UV lithography and dry etched by reactive ion etching, which is stopped when the super lattice below the doped layer is reached. The etch results in straight walls. In the patterned semiconductor wires the charge carriers are located in the doped layer below the surface, which is insulating. They are contacted by alloying: Several metal films are evaporated in defined order and thickness (50 Å Ni, 400 Å Ge, 800 Å Au, 200 Å Ni and 2000 Å Au) onto the regions, where the semiconductor is going to be contacted. The first 4 layers are to be alloyed into the surface and contact the semiconductor, the top gold layer supports enough metal to allow bonding. Alloying is accomplished by a well defined thermal cycle heating the sample up to 430°C [34].

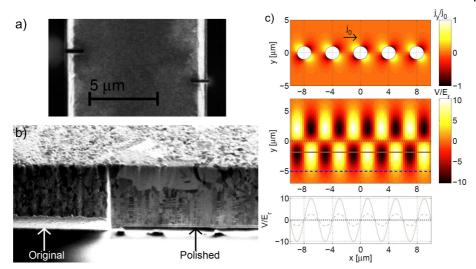

Finally the small GaAs chip is mounted on a standard gold layer carrier atom chip by gluing, and contacted by wire bonding. The atoms are to be trapped and cooled on the carrier atom chip, and then transported to the semiconductor chip. Pictures from a fabricated and mounted chip can be seen in Fig. 1.10.

**Fig. 1.10** Example of an atom chip fabricated in a GaAs substrate. *a*) Central region of the chip. The deep etched trenches defining where the doped layer is removed are shown dark *b*) Wire bonds connected to the alloyed metal pads on the GaAs chip *c*) Overview of the GaAs chip mounted on a carrier chip.

#### 1.5.4

#### **Permanent magnets**

Most atom chips rely on a pattern of current-carrying wires to generate the necessary magnetic fields. By contrast, it is also possible to use patterned films of permanently magnetized material for this purpose (see chapter ??). The ideal magnetic material for use in atom chips has a large remanent magnetization and coercivity, regardless of the shape, is very homogeneous, has a high Curie temperature, is corrosion resistant, and UHV compatible. Several groups have developed fabrication processes for permanent magnet atom chips, see e.g. [10,11,88–95] and references therein, and we discuss a few examples in the following.

Commercial magnetic storage media such as videotape or hard disks provide a convenient way to prepare small magnetic structures. In [88] an atom mirror was fabricated by etching of a common hard drive. The hard drive provides a large area of thin magnetic film whose remnant magnetic field and coercivity can be as large as 7 and 3 kG, respectively. The atom mirror is fabricated by etching 2  $\mu$ m wide, 100 nm deep trenches into the film. Standard photolithography is used to create the etch mask. The cobalt alloy of the magnetic film is granular, which enhances the coercivity and allows one to magnetize the material in plane and parallel to the short axis of the magnetic strips.

In [89] it was demonstrated that a pattern of magnetization recorded in commercial videotape can be used to generate an array of elongated magnetic microtraps. Videotape can store patterns with feature sizes down to a few micrometers using simple commercial recording equipment adapted in the laboratory. It is designed to hold data reliably for long periods of time and has a high coercivity (1500 Oe), making the magnetization insensitive to

the presence of magnetic bias fields. The tape used in [89] has a 3.5  $\mu$ m thick magnetic layer containing iron-composite needles, 100 nm long with 10 nm radius, which are set in a glue and aligned in parallel. The film is supported by a polymer ribbon 11  $\mu$ m thick. Remarkably, the tape is UHV compatible and is able to withstand baking at 120°CThe same group has also investigated various other permanent magnetic materials for atom chips, such as magnetooptically patterned CoPt thin films [90].

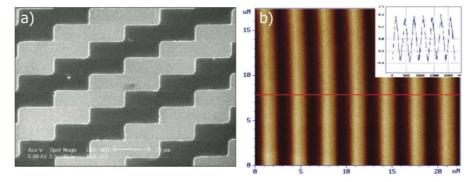

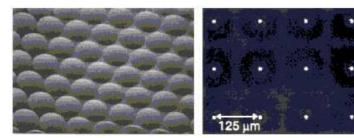

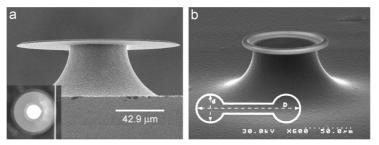

The Amsterdam group has found that FePt is a magnetic material ideally suited for the use in atom chips [10,91-93]. Their first chip was made out of a 40 µm thick foil of FePt [10]. An "F"-like shape was cut out by spark erosion and glued onto a mirror. This produces a self-biasing Ioffe-Pritchard trap. The second generation atom chip uses structures lithographically written into a FePt film [92]. Fig. 1.11a shows a two-dimensional FePt pattern with the magnetization oriented perpendicular to the film, which has been used to create a large two-dimensional array of magnetic microtraps [12]. The 300 nm thick FePt film is grown in the ordered face-centered-tetragonal (fct) phase, which is magnetically hard with high uniaxial anisotropy constant. The measured remanent magnetization is  $M_r = 670 \text{ kA/m}$ , the remanent to saturation magnetization ratio  $M_r/M_s=0.93$ , and the coercivity  $H_c=0.95$  T. After baking for 3 h at 150°C in air, the magnetization had reduced by only 3%, and the film was found to be stable against typical time-varying fields applied in the experiment. The film is patterned using optical lithography and argon plasma etching. After patterning, the film is coated with a 100 nm reflective gold overlayer and magnetized in a 5 T magnetic field.

The Melbourne group uses atom chips based on perpendicularly magnetized multilayered TbGdFeCo/Cr films [11, 94, 95]. These films have a large perpendicular magnetic anisotropy and are suitable for the production of periodically grooved, micron-scale structures. Fig. 1.11b shows an example of a patterned film that can be used to produce a one-dimensional magnetic lattice. To pattern such magnetic films, a periodically grooved structure is first fabricated into a Si substrate by reactive ion etching. The TbGdFeCo film is then deposited on this grooved structure by magnetron sputtering. Because the magnetic anisotropy is found to deteriorate for a film thickness above 250 nm, a multi-layer structure is deposited, consisting of several layers of TbGdFeCo (160 nm) and Cr (100 nm) to achieve a total thickness of about 1  $\mu$ m. A 10 nm Cr film and finally a 150 nm gold film are deposited on top of this structure in order to produce a mirror for the mirror-MOT. Measurements show that the remanent magnetization of the film is about 3 kG and the coercivity is about 6 kOe [95].

**Fig. 1.11** Permanent magnet atom chips. (a) SEM image of the patterned magnetic film of [92]. The light gray areas correspond to the FePt pattern and the darker regions are the Si substrate. The film can be used to create a two-dimensional magnetic lattice potential. (b) Magnetic force micrograph of the patterned magnetic film of [94]. The structure is a 150 nm thick  $Gd_{10}Tb_6Fe_{80}Co_4$  film on a 140 nm thick Cr underlayer on a Si grating structure with a period of 3  $\mu$ m. The grooves are represented by the light regions and the inset shows a cross-section of the MFM signal along the indicated line.

#### 1.5.5

#### Metal outlook

As the fabrication of magnetic field based atom chips evolves in the future, one would also need to look at additional forms of materials. Aside from the above mentioned metals, alloys, superconductors, semi conductors and permanent magnets, it stands to reason that additional classes of new materials will be investigated in the near future. Here, as an example, we shall focus on nano wires, molecules and metallic crystals, which are already being studied in several groups.

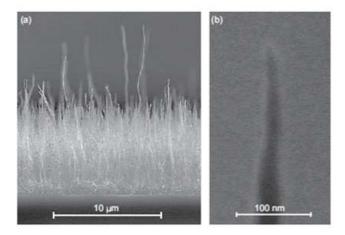

Nano wires (Fig. 1.12) constitute an interesting system. While the current may be sufficiently high to maintain magnetic traps, the Johnson noise may be sufficiently low to enable long spin flip lifetimes at small atom-surface distances. Lifetimes of seconds may be reached for atom-surface distances of less than one micrometer [49]. Fabricating nano wires may only be done through direct e-beam writing, and even then, requires considerable attention to details such as edge roughness and contact resistivities. We note that due to surface scattering, the nano wire resistivity may be high, an issue which may be solved by using crystalline nano wires, namely molecules, which are our next topic.

Molecules may form interesting conductors for numerous reasons. First, they may be able to sustain extremely high current densities. Second, they may suppress hindering effects such as Van der Waals and Casimir-Polder (CP) forces, corrugations due to imperfections causing electron scattering, and

noise giving rise to spin flips, heating and decoherence. Third, molecules have a relatively sharp absorption spectrum and hence may be put much closer to sensitive optical devices in comparison with normal metal wires. Finally, one may also look into a future in which molecules will self assemble into circuits (forming molecular electronics), and similarly may be used to assemble current carrying atom chip circuits.

A specific molecule that has recently attracted attention is the Carbon Nano Tube (CNT). The CNT may hold current densities of up to 10<sup>9</sup> A/cm<sup>2</sup> (two orders of magnitude higher than normal metals), may have ballistic transport (hence negligible scattering causing corrugations) and is also expected to produce less noise and CP forces. Two articles describe the advantages of CNTs [96, 97]. To the best of our knowledge, to date, no atoms have been trapped in the magnetic field of a CNT but several groups, such as the Tübingen group, are pursuing this goal.

CNTs come in different shapes and forms: from single-wall CNTs to multiwall CNTs, from semi-conducting to metallic, and from suspended to substrate based. While a multi-wall CNT offers more current, it is also less crystalline in nature. While a suspended CNT offers less CP it probably also enables less current density due to the lack of a heat sink. It is unclear what the ultimate current limit of single wall CNTs is but while 20  $\mu$ A seem to be enough for trapping at a height of a few hundred nanometers (also taking into account the CP force) [98], experiments at the Ben-Gurion University group show that CNTs of a few  $\mu$ m length are able to carry up to 50  $\mu$ A.

Typically a Chemical Vapor Deposition sample will contain many CNTs with random orientations, lengths, and degrees of straightness. A preliminary survey is taken by AFM and, if suitable CNTs are seen, grids of Ti alignment marks (e.g. 2  $\mu$ m long, 1  $\mu$ m wide, 40 nm thick, 10  $\mu$ m spacing) are grown by e-beam lithography (PMMA resist baked at 200°C) and thermal evaporation over several small areas of the Si wafer. After lift-off with NMP at 80°C these areas are then carefully scanned by AFM; co-ordinates for suitable CNTs are measured with respect to the Ti alignment marks.

The next step is to contact both ends of the CNT with parallel leads in order to form the "Z" shape typically used for Ioffe-Pritchard atom chip micro-traps (and now for CNT-based nano-traps). Pd leads are usually thought to have the best contact resistance to CNTs and are made by using a second e-beam lithography step with PMMA (the same as before) and are typically 30-40 nm thick and 1  $\mu$ m wide, (see Fig. 1.12).

In the future, it is expected that CNTs will be grown in a controlled way along pre-defined paths. One such method, includes growth of CNTs along atomic steps in the substrate [99, 100]. An alternative method for controlling the CNT position and orientation utilizes an imprint process [101]. In such a case where the CNT's position and direction is determined by the user, one

**Fig. 1.12** (a) An AFM scan of a single wall carbon nano tube  $(2\mu m \log 2 + 1)$  long connected to Pd pads [98]. Around  $40\mu A$  were pushed through this CNT. (b) Nano wire: 50nm wide and 20nm thick [49] (fabrication of both samples done at the Ben-Gurion University fabrication facility).

may also etch the substrate before depositing the CNT, evaporate or electroplate a loading wire into the etched channel, deposit an insulating layer and obtain a smooth substrate by Chemical Mechanical Polishing (CMP) or other planarization methods described in this chapter, and then place the CNT on top - hence obtaining a truly monolithic CNT atom chip.

Before moving on, let us note that nano wires and molecules such as CNTs may be used also for other purposes. For example, ideas have emerged where plasmonic waves on such elements may be used to trap and couple light between nearby atoms. Another example, which was realized experimentally, includes utilizing CNTs for high efficiency atom counting. The experiment was conducted in the Tübingen group of J. Fortagh [102]. In Fig. 1.13 we show the CNTs used to create a high electric field for the purpose of ionization and ion counting.

Another class of materials that has so far not been used in atom chips is crystalline metals. There may be several advantages for utilizing such materials. To start with, they may offer reduced electron scattering and thus produce potentials with less corrugation. They may also be used in their electrically anisotropic form to significantly reduce decoherence even at room temperature (Fig. 1.14) [103].

Fabrication of atom chips using these materials is not trivial. To start with, these materials may not be deposited through evaporation and need to be grown in specialized methods. Typically, one can buy layers of these materials after which they will need to be bonded to a substrate (as they usually come as thick leafs or attached to dissolvable substrates), thinned (without causing too much surface roughness) and patterned. Obviously, standard lift-off may not be used here as the photoresist may only be put on top of the material.

Fig. 1.13 Vertical CNTs used to create a high electric field for ionization of neutral atoms. The ions are then detected with single atom precision.

Fig. 1.14 The spin decoherence rate as a function of the electrical anisotropicity of the material [103]. The different lines represent different types of anisotropic materials (see legend). Several material examples are also shown.

Shadow masks followed by wet etching, ion beam milling or plasma etching will need to be utilized. In addition to the above, one would also have to utilize normal evaporated metals to make electrical contacts as the above crystalline materials may not have suitable conductivity in all directions.

**Fig. 1.15** Planarization and insulation with polyimide. Narrow gaps are easier to planarize than broader, isolated features. Multiple coatings improve planarization [41].

# 1.6 Additional features

#### 1.6.1

#### Planarization and insulation

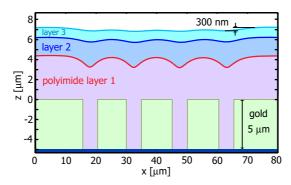

Dielectric layers for planarization and electrical insulation are essential for the fabrication of multi-layer chips. Besides the dielectric and planarization properties, good heat conductivity, ultra-high vacuum compatibility, and chemical stability in subsequent processing steps are important criteria for the choice of suitable materials.

Spin-on polyimide has been used in the multi-layer atom chip designs of [23,41]. It provides good planarization, electrical insulation, and is UHV compatible. Moreover, some polyimides can be directly structured by UV lithography. On the other hand, polyimide has a thermal conductivity which is about three orders of magnitude smaller than that of gold or silicon. Therefore, the polyimide layer has to be as thin as possible to allow for large current densities in the wires of the upper gold layer. To process polyimide, the chip is spin-coated with the polyamic ester. Subsequent curing of the polyimide is carried out at temperatures of typically 300-400°CFully cured polyimide is resistant to solvents and most acids, but can be dry etched in an oxygen plasma [47].

As illustrated in Fig. 1.15, a layer of polyimide does not globally planarize a chip surface with an uneven topography. It rather acts as a "low-pass filter" which locally smoothens out the topography. Only features with a lateral extension smaller than the planarization length, which is  $\sim 20~\mu m$  for the polyimide used in [41], can be fully flattened out [104]. The degree of planarization is higher for several thin coatings compared with a single thick coating of equal total thickness. Fig. 1.16 shows AFM measurements of the polyimide surface topography above gold wire structures. Thin gaps (5  $\mu m$  wide) between 5  $\mu m$  thick wires are planarized to a step height of 300 nm with three layers of polyimide. If necessary, the thickness of the polyimide could be reduced by subsequent back-etching.

Fig. 1.16 Planarization results [41]. Surface topography of three polyimide layers above small gaps in a lower gold layer, measured with an AFM. Note the different scaling of the two axes. On this chip, the polyimide layers were 4.3, 1.9, and  $1.0\mu m$  thick.

#### 1.6.2

### **On-chip mirrors**

It is often desirable to have a high-quality mirror as the uppermost layer on the atom chip. A mirror is required for the operation of a mirror-MOT [36]. Moreover, it enables imaging of the atoms very close to the chip surface, using an absorption imaging beam that is reflected from the surface [105]. The mirror can also be used for reflecting laser beams that generate optical dipole traps.

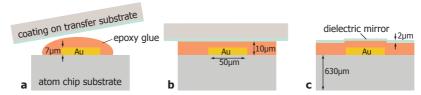

High-quality dielectric mirror coatings can be transferred to the chip using a replica technique [106, 107], which is illustrated in Fig. 1.17. In this technique, a detachable mirror coating supplied on a transfer substrate is glued onto the desired chip area using vacuum-compatible epoxy glue. The transfer substrate is manually removed, leaving the coating on the atom chip. Various types of dielectric coatings on transfer substrates are commercially available. By cutting the transfer substrate to the desired size, it is possible to only partially cover the atom chip with the mirror [29,108]. The transfer technique can also be used for homogeneous metal layers [106]. The advantage compared to evaporating the metal layer is that pretty good planarization of underlying structures can be achieved.

Covering the uppermost wire layer with a dielectric mirror or metal mirror on a dielectric spacer is not always desired. The mirror layer increases the minimum distance of the atoms to the wires, thereby reducing the attainable field gradients. If the uppermost wire layer contains microwave guiding structures, the mirror changes the waveguide impedance and introduces additional losses or shields the atoms from the microwave field. In these cases, a viable option is to use the uppermost wire layer itself as a mirror [20,44]. This requires high-quality metal deposits and narrow gaps between the wires.

**Fig. 1.17** Fabricating a dielectric mirror on the atom chip using the transfer technique [106, 107]. (a) A small drop of UHV-compatible epoxy glue is dispensed on the atom chip. (b) The transfer substrate with the dielectric coating is sandwiched onto the chip. (c) After curing the epoxy, the transfer substrate is lifted off, leaving the dielectric mirror on the atom chip. On a structured chip, epoxy shrinking causes small modulations of the mirror surface.

Experiments have shown that a mirror MOT is remarkably tolerant against the distortions of the light field caused by the gaps, even for gap sizes of the order of 10  $\mu$ m. However, the gaps between wires cause clearly visible distortions on high-resolution absorption images taken with light reflected from the mirror.

Even if no dielectric mirror is desired, it can be advantageous to cover the uppermost metal layer on the chip by a few nanometers of a dielectric such as SiO<sub>2</sub>. This prevents alkali atoms from contaminating the metal layer over time and degrading its reflectivity or even creating shortcuts between wires. A thin SiO<sub>2</sub> layer could also reduce the electric fields from alkali adsorbates on the surface.

#### 1.6.3

#### Multi-layer chips

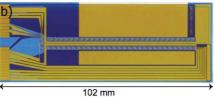

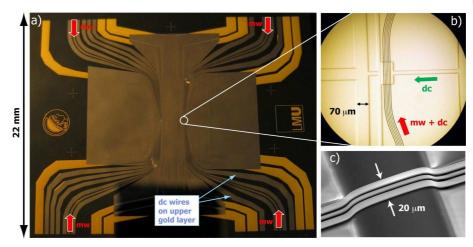

Many applications of atom chips in both fundamental science and technology require chips with complex multi-layer wire patterns. A multi-layer chip allows for much greater flexibility in trap design by avoiding wire crossings which would arise in a single layer. This is crucial e.g. for experiments on quantum information processing, which will eventually require large arrays of qubits in individually addressable microtraps on a single chip (see chapter ??). Some proposals for quantum gates require the integration of microwave guiding structures on the chip in addition to the already complex DC wire structures [17,20]. Moreover, it is often necessary to combine wires of very different size and thickness on the same chip, e.g. because the experimental sequence starts with an ensemble of atoms in a large-volume trap, while the actual experiment is performed with a small Bose-Einstein condensate in a micrometer scale trap. In all these cases, multiple wire layers separated by dielectric insulation layers are beneficial. Here we discuss several examples

Fig. 1.18 (a) Atom chip of [22]. Three different experiment chips with micrometer size structures are glued on top of a carrier chip with larger structures for positioning of the atoms. (b) Atom chip of [108]. This magnetic conveyor belt is a two-layer structure with vias, fabricated by thick-film hybrid technology.

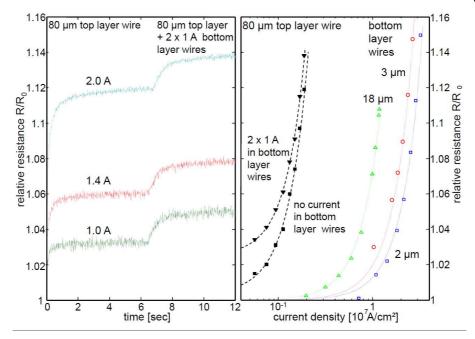

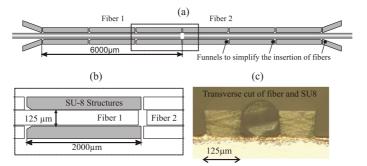

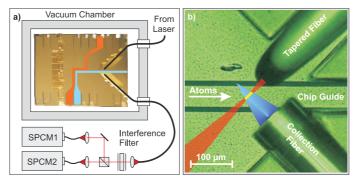

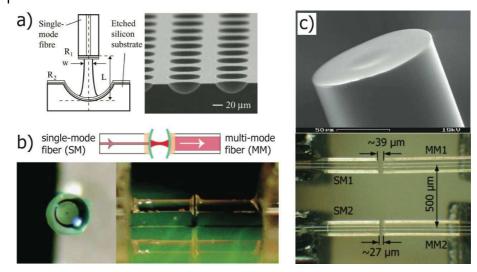

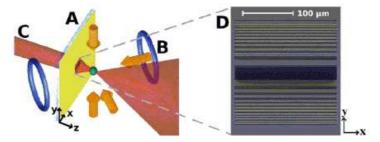

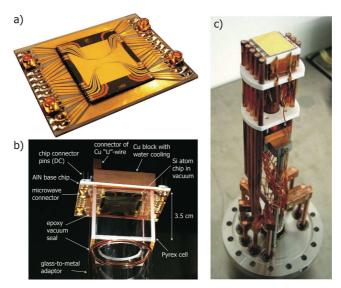

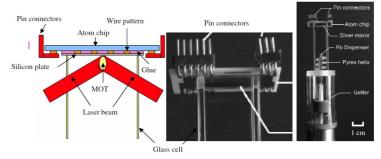

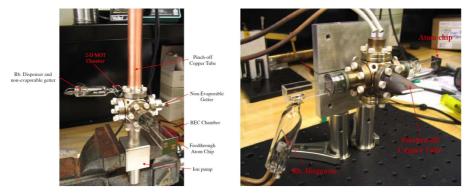

of multi-layer atom chips which have been used in experiments. A general introduction to multi-layer microfabrication is given in [104].